本次美国代写是关于模拟集成电路相关的一个Assignment

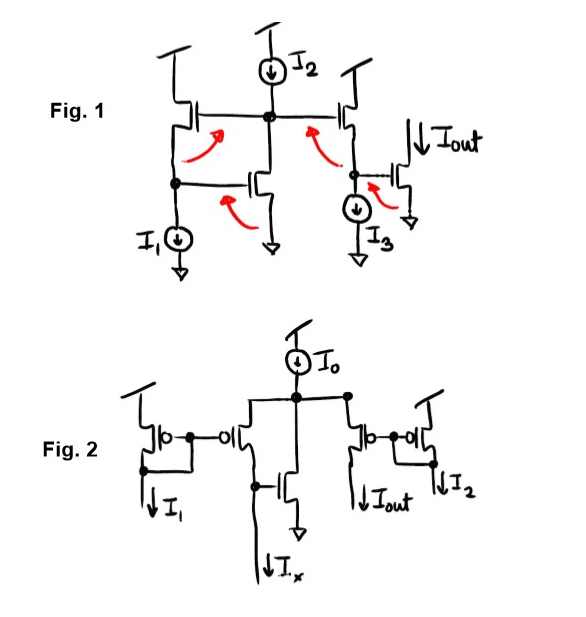

In this assignment you will be simulating a sub-threshold analog multiplier circuits shown in Fig. 1 and Fig. 2. You could choose the width and length of all the transistors to be 60 µm and 30 µm respectively. Assume Vdd = 3V.

1. Use DC analysis sweep the input current I1 in Fig. 1 and plot Iout as a function of the other bias currents I2 and I3. Explain using translinear equations any deviation from the ideal response [10 point].

2. Use DC analysis sweep the input current Ix in Fig. 1 and plot Iout as a function of the other bias currents I1 and I2. Explain using translinear equations any deviation from the ideal response. You have to pay attention to biasing to make this circuit work [10 point].